Télécharger en format PDF

Exercice 1

- Combien de bascules sont nécessaires pour le MAR et le MBR d’une mémoire 1 K*4 bits?

- Combien de mots, devrait contenir une mémoire si son MAR est de 8 bits?

- En utilisant comme unité des RAM 256*4 bits, concevoir une mémoire de :

- 1 K*4 bits

- 1 K*8 bits.

Solution

Exercice 2

On dispose d’une machine dont le bus d’adresse est sur 16 bits et le bus de données est sur 8 bits. La mémoire de cette machine est composée d’une RAM de 32 Kilo*8 et d’une ROM de 16 Kilo*8.

- Quelle est la taille des registres d’adresse MAR et MBR ?

- Donner le schéma fonctionnel de cette RAM en utilisant des mémoires de 32 K x 4 bits

- Donner le schéma fonctionnel global (RAM+ROM), en précisant les adresses de chaque boitier.

Solution

Exercice 3

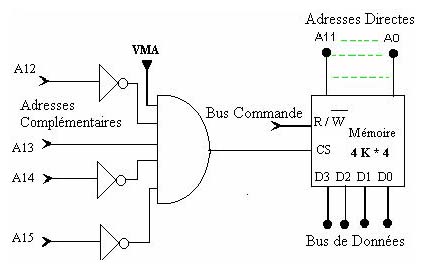

Soit une mémoire RAM de 4 Kilos*4 représentée par le schéma suivant :

- Quel est le rôle des brôches R/W et CS dans un circuit mémoire ?

- De combien de bits est constituée la donnée stockée dans cette mémoire ?

- De quelle capacité est cette mémoire(en Kbits puis en Koctets) ?

- Quel doit être l’état du signal VMA (Valid Memory Access) et l’état des lignes A12 à A15 pour sélectionner cette mémoire ?

- Donner la plage d’adresses (en Héxadécimal) utilisée par cette mémoire.

- On veut augmenter la taille de la donnée à 16 bits en associant plusieurs mémoires 4K*4. Donner le branchement nécessaire.

Solution

Exercice 4

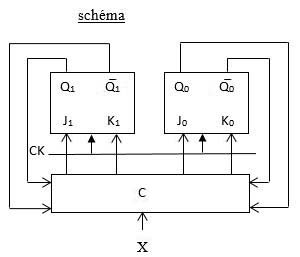

Soit un circuit défini par le fonctionnement et le schéma bloc suivant :

Fonctionnement :

Qt1 |

Qt0 |

X |

|

Q1t+1 |

Q0t+1 |

0

0 |

0

0 |

0

1 |

|

0

0 |

0

1 |

0

0 |

1

1 |

0

1 |

|

1

0 |

0

1 |

1

1 |

0

0 |

0

1 |

|

1

1 |

0

1 |

1

1 |

1

1 |

0

1 |

|

1

0 |

1

0 |

- Réaliser le circuit C permettant de donner (J0, K0) et (J1, K1).

- On veut réaliser le même fonctionnement en utilisant des bascules D au lieu des bascules JK et une mémoire ROM au lieu du circuit C.

Donner la table de vérité et le nouveau schéma bloc (préciser bien les entrées/sorties). Combien de bits sont demandés dans la ROM ?

Solution

Exercice 5

1. Etablir la table de vérité d'un additionneur complet à 2 bits.

2. Réaliser le circuit d'un additionneur complet à 2 bits à l'aide d'une ROM.

Solution

Exercice 6

On considère une machine avec la configuration suivante : une mémoire centrale de 2 MO, avec des mots mémoires de 4 octets et un bus d'adresses de taille 20 bits.

- Calculer la taille minimale du bus d'adresses qui permet d'adresser cette mémoire.

- Déterminer la plage d'adressage de cette mémoire (adresse minimale et adresse maximale en Hexa.)

- En fait, cette mémoire est constituée de deux blocs séparés. Le premier est une RAM de taille 1 M octets de mots de 4 octets adressable à partir de l'adresse (00000)16 et le deuxième est une ROM de taille 1 M octets de mots de 4 octets adressable à partir de l'adresse (40000)16.

- Donner le schéma de la mémoire en montrant les connexions nécessaires.

- Déterminer les deux plages d'adressage respectivement de la RAM et la ROM.

- Est-ce que la mémoire centrale de cet ordinateur est extensible ? Si oui, déterminer la taille de la mémoire d'extension et le nombre minimum de blocs mémoires (de même taille que les précédents) qu'on peut y rajouter ? Justifier.

Solution

Exercices complémentaires

Exercice 7

Soit les fonctions définies comme suit :

F1(xyz) = xy + yz + xz

et F2(xyz) = xyz + zx

On veut sauvegarder les valeurs de ces fonctions dans une mémoire, de sorte à ce qu’on puisse récupérer la valeur de F1 et F2 en introduisant (xyz) comme adresse.

- Donner le type et la capacité de cette mémoire.

- Tracer la structure interne de cette mémoire.

Solution

Exercice 8

On veut réaliser une table de division par 3 à l’aide d’une ROM. On se restreint à la division des nombres 0, 1, 2,…, 15 par 3. A la sortie, on veut récupérer le quotient entier de la division.

- Quelle doit être la taille minimum de la ROM à utiliser ? Expliquer pourquoi.

- Calculer les fonctions (simplifiées) réalisées par cette ROM.

- Réaliser le circuit logique associé.

Solution