1. Table des transitions ou d’états:

| Etat Initial |

X1X0 | |||||||

|---|---|---|---|---|---|---|---|---|

| 00 | 01 | 10 | 11 | |||||

| EF | Y | EF | Y | EF | Y | EF | Y | |

| A | B | X | A | 1 | A | 0 | C | X |

| B | B | 0 | A | X | B | 0 | C | X |

| C | C | 0 | A | X | D | X | C | 1 |

| D | C | X | A | X | B | X | D | 1 |

2. Codes des états (Q1Q0):

A → 00 ; B → 01 ; C → 10 ; D → 11

3. Table d’excitation avec des bascules T :

| X1 | X0 | Q1 | Q0 | Q1+ | Q0+ | Y | T1 | T0 |

|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 1 | X | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 1 | 0 | X | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 | 0 | X | 0 | 1 |

| 0 | 1 | 1 | 0 | 0 | 0 | X | 1 | 0 |

| 0 | 1 | 1 | 1 | 0 | 0 | X | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 1 | X | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | 1 | X | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | X | 1 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | X | 1 | 1 |

| 1 | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 | 0 |

4. Equations simplifiées :

Q1Q0

X1X0 |

00 | 01 | 11 | 10 |

|---|---|---|---|---|

| 00 | X | 0 | X | 0 |

| 01 | 1 | X | X | X |

| 11 | X | X | 1 | 1 |

| 10 | 0 | 0 | X | X |

Y = X0

Q1Q0

X1X0 |

00 | 01 | 11 | 10 |

|---|---|---|---|---|

| 00 | 0 | 0 | 0 | 0 |

| 01 | 0 | 0 | 1 | 1 |

| 11 | 1 | 1 | 0 | 0 |

| 10 | 0 | 0 | 1 | 0 |

_ _ _ T1 = X1 X0 Q1 + X1 X0 Q1 + X1 X0 Q1 Q0

Q1Q0

X1X0 |

00 | 01 | 11 | 10 |

|---|---|---|---|---|

| 00 | 1 | 0 | 1 | 0 |

| 01 | 0 | 1 | 1 | 0 |

| 11 | 0 | 1 | 0 | 0 |

| 10 | 0 | 0 | 0 | 1 |

_ _ _ _ _ _ _ _ T0 = X1 X0 Q1 Q0 + X0 Q1 Q0 + X1 Q1 Q0 + X1 X0 Q1 Q0

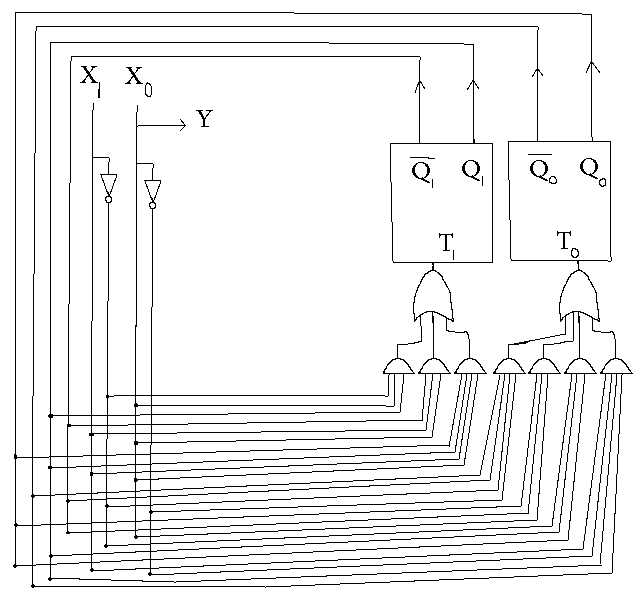

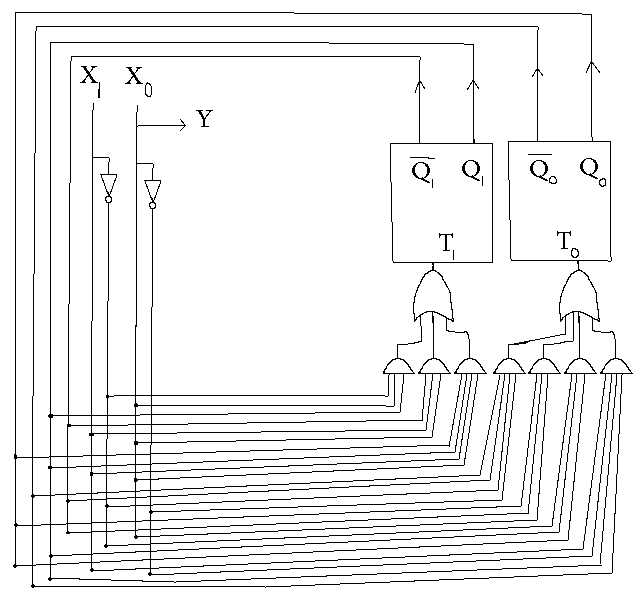

4. Circuit :

Taille MAR = 10 bits; Taille MBR = 8 bits.

2. Taille de la mémoire totale

Nombre de mots mémoire = 210 = 1024 mots

Taille en bits = 1024 x 8 = 8192 bits = 213 bits

Taille en K bits = 210 x 8 = 8 K bits

Taille en K Octets = (210 x 8) / 8 = 1 K Octets

3. Nombre de blocs mémoire

= (Taille totale / Taille Bloc )

= (213 bits) / ( 256 * 4 bits)

= (213) / ( 210) = 23 = 8

Nombre de colonnes verticales = 8 / 4 = 2

Nombre de niveaux (lignes horizontales) = 8 / 2 = 4

4. Répartition dans les blocs mémoire :

La méthode la plus simple est de convertir les adresses de la mémoire en héxadécimal. Puisque chaque bloc mémoire a un MAR de 8 bits, il résulte que les bits 9 et 10 de chaque adresse désigne directement le niveau du bloc mémoire associé :

(254)10 → (0FE)16 ;

(255)10 → (0FF)16 ;

(256)10 → (100)16 ;

(641)10 → (281)16 ;

(689)10 → (2B1)16 ;

(837)10 → (345)16 ;

D'où :

| Contenu Colonne 1 & Colonne 2 | |

|---|---|

| Niveau 0 | LOAD 641, D MUL 7, IMM |

| Niveau 1 | STORE 689, IND |

| Niveau 2 | 20 837 |

| Niveau 3 | 30 |

5. Déroulement :

| CO | RI | ACC | MAR | MBR | @837 |

|---|---|---|---|---|---|

254 |

? |

? |

? |

? |

30 |

255 |

LOAD D |

20 |

641 |

20 |

30 |

256 |

MUL IMM |

20 * 7 = 140 |

255 |

MUL 7, IMM |

30 |

257 |

STORE IND |

140 |

837 |

30 |

140 |