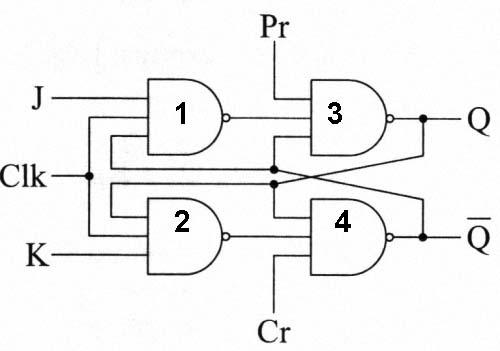

1. Montrer qu'une Remise à Un (RAU : Cr=1 et Pr=0) de la bascule J-K ne peut se faire correctement que si [K] + [Clk]=1

Que se passerait-il si la condition n'était pas vérifiée ?

L'inverse de la condition [K] + [Clk] =1 est K . Clk =1, et donc on devrait avoir alors K = Clk = 1.

les 2 propositions sont incohérentes et conduisent à un état indéterminé lorsque Pr revient à 1 (fonctionnement normal de la bascule)

Il faut donc avoir [K] + [Clk] = 1

2. Montrer qu'une Remise à Zéro (RAZ : Cr=0 et Pr=1) de la bascule J-K ne peut se faire correctement que si [J] + [Clk] =1

un raisonnement symétrique du précédent conduit à la nécessité de [J] + [Clk] =1 pour pouvoir faire correctement une remise à Zéro

3. Qu'en concluez vous sur l'usage des entrées asynchrones ?

les entrées asynchrones Cr et Pr ne peuvent être utilisées de façon déterministe que quand Clk = 0.

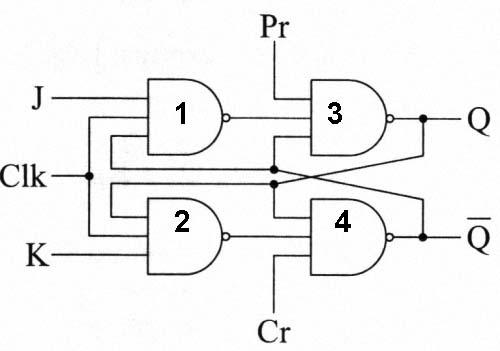

Nous considérons une bascule J-K maître-esclave dans l'état initial Q=0 et [Q]=1

Compte tenu de l'état initial de la bascule (Q=0), on doit avoir QM =0 avant l'arrivée du signal d'horloge (l'état de Q est celui qu'avait QM avant l'arrivée du tick d'horloge précédent). De plus, en fonctionnement normal, Pr=Cr=1.

1. Que devient QM lorsque Clk=1, J=0, K étant dans un état quelconque ?

Si J=0, la sortie de la porte NAND 1 est forcément 1

toutes les entrées de la porte NAND 3 sont à 1 ⇒ la sortie de la porte 3 est à 0 et par conséquent :

( J= 0, Pr =1, [QM]=1 ) ⇒ QM = 0 et l'état est stable

2. Que devient QM si J passe dans l'état 1 ?

pour que le changement de valeur de J soit visible pour la première partie de la bascule, il faut que Clk soit à 1.

( J=1, Clk =1, [Q]=1 ) : les trois entrées de la porte NAND 1 sont à 1, sa sortie est donc à 0 ⇒ QM=1 et [QM] =0 (les 3 entrées de la porte 4 sont à 1). L'état est stable.

3. Que devient QM si J revient dans l'état 0 ? Qu'en concluez vous ?

J=0 mais [QM] = 0 ⇒ QM=1 et l'état est stable

QM ne revient donc pas dans son état initial. Nous pouvons en conclure que les entrées J (et K) doivent être stabilisées avant l'arrivée du signal d'horloge et ne pas varier pendant la durée de l'impulsion.

La figure suivante donne le chronogramme des signaux appliqués aux entrées J, K et Clk d'une bascule J-K maître-esclave. En supposant que la bascule est dans l'état Q=0 avant l'arrivée du premier signal d'horloge, tracer le chronogramme des sorties Q et [Q] (les entrées asynchrones sont dans l'état Pr = Cr = 1)

Nous pouvons écrire la table de vérité à chaque front descendant de l'impulsion horloge : n

ce qui donne

1. Vérifier qu'une bascule R-S-T est convertie en bascule de type T si S est connectée à [Q] et R à Q

Le montage proposé est

A partir de la table de vérité de la bascule R-S, nous pouvons écrire Qn

on retrouve la relation caractéristique d'une bascule T : Qn+1=[Qn]

2. Vérifier qu'une bascule de type D devient une bascule de type T si D est connectée à [Q].

le montage est

La table de vérité est

on retrouve encore Qn+1=[Qn]

Montrer comment réaliser une bascule A-B dont la table de vérité est donnée ci-dessous, en utilisant une bascule J-K et toute la logique nécessaire

A partir de la table de vérité de la bascule A-B, nous pouvons définir les valeurs que doivent avoir les entrées J et K pour fournir le résultat attendu :

On en déduit les expressions de J et K en fonction de A et B :

d'où le logigramme

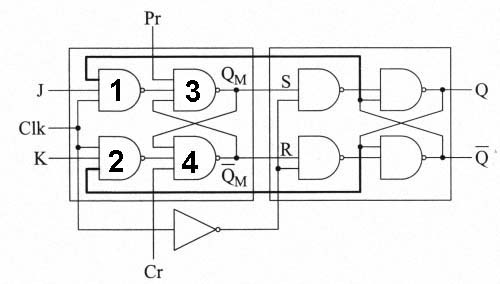

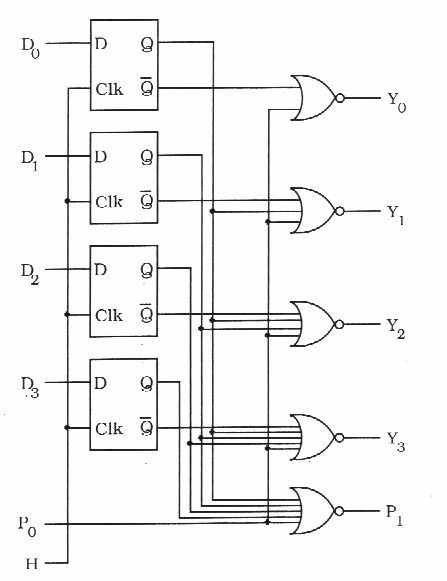

VI Registre prioritaire cascadable

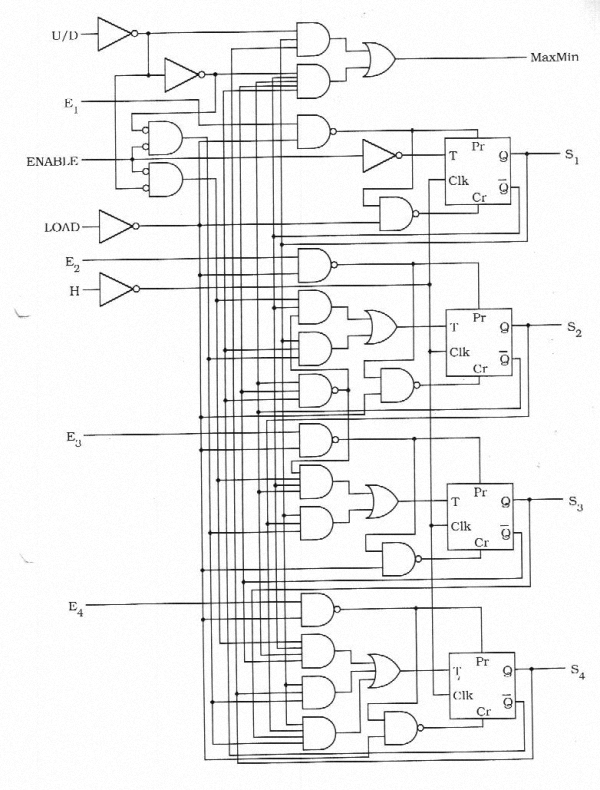

Le schéma suivant représente un registre prioritaire cascadable de 4 bits

Après un signal de chargement donné par H, nous retrouvons les entrées D sur les sorties Q de chaque bascule D. compte tenu de la logique combinatoire définissant les sorties Y à partir des sorties Q et [Q] de chaque bascule, nous pouvons écrire :

1. Posons : P0 = 0, D0 = D1 = D3 = 0 et D2 = 1. Vérifier que Y2 = 1 et que toutes les autres sorties sont à 0.

A l'aide des relations précédentes, on calcule immédiatement: P1=0, Y0 = Y1 =Y3 = 0 et Y2 = 1

2. Posons : P0 = 0, D0 = D1 = 0 et D2 = D3 = 1. Vérifier que Y2 = 1 et que toutes les autres sorties sont à 0.

On obtient encore P1=0, Y0 = Y1 =Y3 = 0 et Y2 = 1

3. Généraliser les résultats précédents en montrant qu'une seule ligne de sortie Yi peut être dans l'état 1, celle ci correspondant à l'entrée Di de plus bas poids dans l'état 1.

Supposons que :

alors, compte tenu des relations liant les entrées aux sorties, on a P1 =0

4. Comment cascader deux circuits de ce type pour obtenir un registre prioritaire de 8 bits ?

Si toutes les entrées sont à 0, seule P1 est à 1. D'autre part, si P0 est à 1, toutes les sorties sont à 0.

Ceci suggère le montage suivant :

Si une des quatre premières entrées au moins est à 1, celle d'ordre le plus bas est repérée par la sortie Y correspondante. P1 étant à 0, alors le second registre est bloqué avec toutes ses sorties à 0

Si aucune des quatre premières entrées n'est à 1, les quatre sorties Y correspondantes sont à 0 et P1=1.

Le second registre peut alors jouer son rôle et repérerl'entrée de poids le plus bas dans l'état 1.

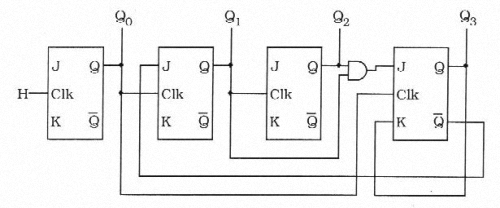

Soit le compteur correspondant au diagramme logique suivant (les bascules J-K maître-esclave effectuent leur transition quand le signal d'horloge passe de 1 à 0) :

1. Ecrire la table de vérité des sorties Q0, Q1, Q2 et Q3, en partant de 0000 après chaque impulsion d'horloge. Quand aucune connexion n'est visible, il faut comprendre que l'entrée correspondante est toujours dans l'état 1. Vérifier qu'il s'agit d'un compteur modulo 10.

La bascule 0 ayant ses entrées J et K en permanence à 1 change d'état à chaque impulsion de l'horloge H. Les bascules 1 et 3 sont commandées par les transitions 1 → 0 de Q0, les états des entrées J et K à prendre en compte étant ceux qui étaient présents quand Q0 = 1. La bascule 2 ayant ses deux entrées à 1 va changer d'état à chaque transition 1 → 0 de la sortie Q1.

On part de la situation initiale :

On en déduit les valeurs des entrées J et K pour les bascules 1 et 3 à prendre en compte pour le top d'horloge suivant :

On en déduit les nouvelles valeurs des sorties Q :

Les nouvelles valeurs des sorties Q permettent de calculer les valeurs des entrées J et K

Q0 passe de 1 à 0, provoquant le changement d'état de Q1. On a les nouvelles valeurs des sorties Q : Q0

et ainsi de suite, d'où la table de vérité complète :

On vérifie que les sorties du compteur décrivent de manière cyclique les chiffres de 0 à 9

2. Comment peut-on utiliser ce système en compteur modulo 5 ?

On peut obtenir un compteur modulo 5 de fréquence deux fois plus faible en n'utilisant que les sorties Q3, Q2 et Q1.

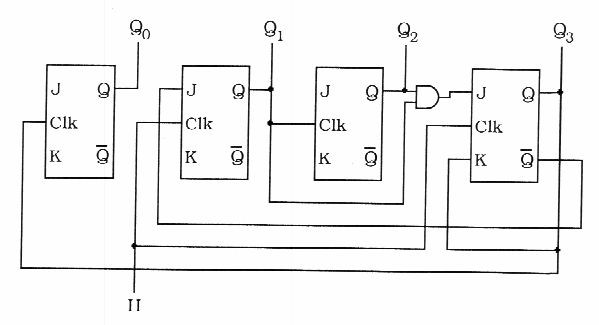

Soit le compteur asynchrone correspondant au diagramme logique suivant :

Les bascules 1 et 3 sont commandées par le signal d'hologe H. Parce que ses 2 entrées J et K sont à 1, la bascule 2 change d'état à chaque transition 1→ 0 de la sortie Q1. De même la bascule 0 qui a aussi ses deux entrées J et K à 1 change d'état à chaque transition 1→ 0 de la sortie Q3.

1. Ecrire la table de vérité des sorties Q0, Q1, Q2 et Q3, en partant de 0000 après chaque impulsion d'horloge. Quand aucune connexion n'est visible, il faut comprendre que l'entrée correspondante est toujours dans l'état 1. Vérifier qu'il s'agit d'un compteur modulo 10.

Pour les bascules 1 et 3, les valeurs de J et K à prendre en compte sont celles de l'état précédent du compteur

2. Ce compteur est dit “biquinaire” (deux fois cinq) car la sortie Q0 ne change d'état que toutes les 5 impulsions. Votre table de vérité doit vérifier cette dénomination.

Nous obtenons un compteur modulo 10 décrivant la séquence 0,2,4,6,8,1,3,5,7,9,0

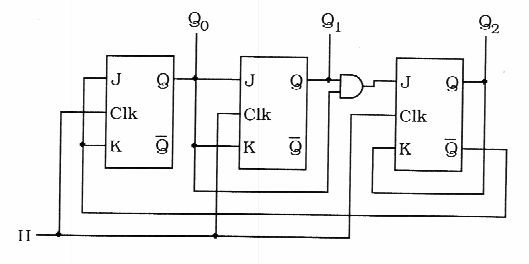

Soit le compteur synchrone correspondant au diagramme logique suivant :

1. Ecrire la table de vérité des sorties Q0, Q1 et Q2 en partant de 000 à chaque impulsion de l'horloge.

On a

On peut alors écrire la table de vérité

2. A quoi correspond ce compteur ?

C'est un compteur modulo 5 qui décrit la séquence 0, 1, 2, 3, 4.

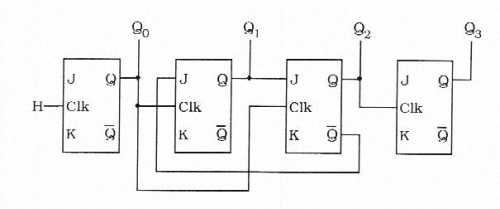

Soit le compteur asynchrone correspondant au diagramme logique suivant :

1. Ecrire, en la justifiant, la table de vérité des sorties Q0, Q1, Q2 et Q3 en partant de 0000 après chaque top d'horloge. De quel type de compteur s'agit-il ?

Leurs entrées J et K étant à 1, les bascules 0 et 3 changeront d'état à chaque réception d'un signal d'horloge valide (horloge H pour 0, transition 1 →0 de Q2 pour 3)

J1= [Q2]

J2=Q1

D'où la table de vérité :

C'est un compteur asynchrone modulo 12 décrivant la séquence : 0, 1, 2, 3, 4, 5, 8, 9, 10, 11, 12, 13

2. Comment peut-on utiliser ce système en compteur modulo 6 ?

Il suffit de n'utiliser les sorties Q2Q1Q0 pour avoir un compteur modulo 6 décrivant la séquence 0, 1, 2, 3, 4, 5

Soit le compteur réalisé avec des bascule T de type maître-esclave correspondant au diagramme logique suivant

1. Pour chacune des bascules, exprimer l'état des entrées asynchrones Pri et Cri en fonction des entrées LOAD et Ei

Compléter la table de vérité suivante

Quelle est la fonctionnalité associée à l'entrée LOAD ? Dans quel état doit-elle être en fonctionnement normal du compteur ?

On a donc Qi = Ei lorsque LOAD = 0. Lorsque l'entrée LOAD est à 0, le compteur est chargé avec les valeurs présentes sur les lignes Ei

En mode de fonctionnement normal, on doit avoir Pr = Cr =1 sur chacune des entrées, ce qui correspond à LOAD = 1

2. Donner l'epression logique de l'entrée Ti de chacune de ces bascules

3. Quel est l'état de chacune de ces entrées Ti lorsque l'entrée ENABLE du compteur est dans l'état "1"? Que peut-on en conclure sur la fonctionnalité de cette entrée ENABLE ? Dans quel état doit-elle être en fonctionnement normal du compteur ?

Lorsque ENABLE = "1", alors T1 = T2 = T3 = T4 = "0"

Chaque bascule reste dans le même état et est donc insensible à la réception du signal d'horloge. Le compteur est bloqué. en fonctionnement normal, on doit donc avoir ENABLE = "0"

4. En mode de fonctionnement normal, sur quelles transitions du signal d'horloge H se font les changements d'état du compteur ?

Le front sur lequel déclenchent les bascules T n'est pas précisé sur le dessin. On peut donc supposer qu'il s'agit du front descendant. L'entrée Clk de chacune des bascules étant reliée à [H] les changements d'état du compteur se produisent sur les transitions 1 → 0 de [H] donc sur les transitions 0 → 1 de l'horloge H.

5. Lorsque l'entrée U/D est dans l'état "1", donner la table des transitions du compteur en supposant chaque bascule initialement dans l'état "0". De quel type de compteur s'agit-il ?

Supposons que l'entrée U/D soit dans l'état "1". Les relations définissant les Ti deviennent :

La table de vérité est alors :

Il s'agit d'un compteur modulo 10 opérant en mode décroissant.

6. Même question quand l'entrée U/D est dans l'état “0 ”. En déduire la fonctionnalité de l'entrée U/D.

La table de vérité est alors :

Il s'agit d'un compteur modulo 10 fonctionnant en mode croissant.

L'entrée U/D détermine le sens de fonctionnement du compteur.

7. Donner l'expression logique de la sortie MaxMin. Pour quelles valeurs du compteur cette sortie est-elle dans l'état “1” ? En déduire son intérêt.

Quand U/D = “ 1” (mode décompteur), Max Min vaut “1” unniquement quand le compteur est à 0 (valeur minimale).

Quand U/D = “ 0” (mode compteur), MaxMin vaut “ 1” unniquement quand le compteur est à 9

(valeur maximale).